Complete Verilog Hdl Programming With Examples And Projects

Posted on 17 Jun 04:21 | by LeeAndro | 19 views

Last updated 6/2022MP4 | Video: h264, 1280x720 | Audio: AAC, 44.1 KHzLanguage: English | Size: 3.45 GB | Duration: 8h 3m

Fundamentals, Design flow, modeling levels, Datatypes, test bench, Tasks & system tasks, FSM, FPGA & examples & Projects

What you'll learn

Learning Verilog HDL Programming fundamental concepts and properties compare to C Language, feature & advantages of Verilog HDL over VHDL

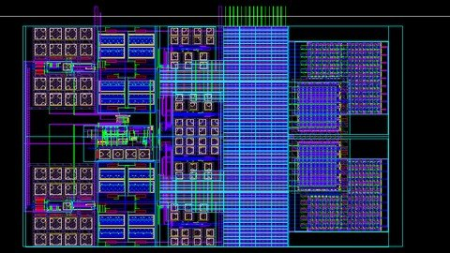

VLSI Design flow ( FPGA & ASIC) and Difference between FPGA vs ASIC

Different design methodologies in Verilog HDL programming with examples

Behavioral modeling with blocking & Non-Blocking concepts and real examples

Test bench Verilog program with examples

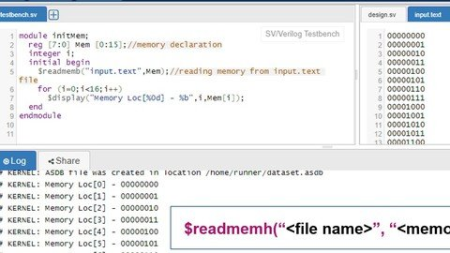

Task & system tasks with examples for random data generator, file based operations and memory load operations, and file representation input & output etc.

Finite state machine (FSM) with example for both Mealy & Moore and Sequence detector FSM

Complete design & test bench programming for Memory controllers

Complete design & test bench programming for FIFO controller

Complete design & test bench programming for Encoder & decoder for Hamming code Error detection correction

Basics of FPGA

Requirements

Intension to learn

basic in C Language

basics in Digital design ( not compulsory)

Description

Complete Verilog HDL programming course with a perfect, well structured and concise course for freshers and experienced, as it is from fundamental level to the application level. This course discuss the concepts in Verilog HDL programming and properties compared with C-Language and discussing the features and advantages. In this course we give information related to VLSI design flow for FPGA & ASIC and gives overview about both.This course gives information on different styles of programming like Gate level, Data flow, Behavioral and switch level with examples. This course gives clear picture on verification, i.e. simulation and writing a test bench and some general examples like counter, clock diver using counter, pulse generator. This courses explains how to write verification models using test benches with task and system tasks with Examples. These examples includes, file based system tasks such as writing data in to file, reading data from file and loading data in to memory and random data generator. This courses shows clear picture on Finite State Machines (FSM) how to draw, how to realize it in to hardware model how ro translate in to verilog code for both Mealy & Moore FSM with examples. This course also shows some projects like Memory controller, FIFO controller and Error detection & correction using Hamming code, this improves ability to analyse and approach to Projects. Finally it gives basic knowledge on FPGA's like core concept how bit file is loaded in to FPGA.

Overview

Section 1: Introduction to the course

Lecture 1 Preview - course content

Lecture 2 Sample program on edaplayground

Section 2: Introduction to Verilog HDL

Lecture 3 Verilog fundamentals

Section 3: VLSI design flow ( FPGA & ASIC)

Lecture 4 VLSI Design flow (FPGA & ASIC)

Lecture 5 FPGA vs ASIC

Section 4: Three levels of verilog design Description

Lecture 6 Three levels of verilog design Description

Lecture 7 Example: mux_2x1 with 3 abstracts models

Section 5: Verilog Language constructs, Data types & Compiler Directives

Lecture 8 Language constructs -Comments, keywords, identifier, Number specific, Operators

Lecture 9 Datatypes - net,reg, integer, real, string, , Parameter, Vector,Array,Memory

Lecture 10 Compiler Directives

Section 6: Verilog Program structure

Lecture 11 Verilog Program Structure -Module

Lecture 12 Ports

Lecture 13 Port Connection Rules

Lecture 14 Design Methodologies Approaches

Section 7: Gate level modeling

Lecture 15 Gate Level Model Introduction

Lecture 16 Example: 4x1 Mux

Lecture 17 Example: Full Adder

Lecture 18 Tri-state Buffers with Examples

Lecture 19 Array of Instance with example

Section 8: Data flow modeling

Lecture 20 Data flow Modeling : assign statement

Lecture 21 Operators

Lecture 22 Arithmetic Operators

Lecture 23 Logical Operators

Lecture 24 Example : Full Adder: Logical operators

Lecture 25 Example : Full Adder: Arithmetic operators

Lecture 26 Example: Binary to Gray code converter

Lecture 27 Logical and , Logical or (&&, )

Lecture 28 Shift operators : Left/right Shift

Lecture 29 Shifting without shift operator , just with concatenation operator

Lecture 30 Ternary operator : Example : 2x1 MUX, 4x1 MUX

Lecture 31 Relational operators Example: Comparator

Lecture 32 Equality , case Equality operators

Lecture 33 Reduction operator : Example: Parity Generator

Section 9: Behavioral Modeling

Lecture 34 Behavioral Modeling - Introduction

Lecture 35 Behavioral Modeling Constructs

Lecture 36 Procedural Blocks- initial & always

Lecture 37 Example: Clock Generation

Lecture 38 Assignment Statements - Blocking & Non-blocking

Lecture 39 Mechanism in Non-blocking

Lecture 40 Concurrency

Lecture 41 Advantage of Non-blocking assignment: Example: swapping

Lecture 42 Advantage of Non-blocking assignment: Example : Pipelining

Lecture 43 if-else: statement: Example : 4x1 Mux

Lecture 44 Case – statement : Example : 4x1 Mux

Lecture 45 Advantage of Case over if-else

Lecture 46 Loops: while, for, repeat, forever

Lecture 47 Parallel blocks - fork-join

Lecture 48 Combinational Logic circuits: List of Examples

Lecture 49 Example: 8x1 mux with 4x1 and 2x1

Lecture 50 Example: AND gate using 2x1 Mux

Lecture 51 Example: 1x8 Demux

Lecture 52 Example: Full Adder & 4-bit Full Adder

Lecture 53 Example : 3x8 Decoder and 3x8 Decoder using 2x4 decoder

Lecture 54 Example : 8x3 encoder

Lecture 55 Example : Priority encoder

Lecture 56 Example : Seven Snt Display

Lecture 57 Example : ALU

Lecture 58 Sequential Logic Circuits: List of Examples

Lecture 59 Example: D Flip Flop vs D-Latch

Lecture 60 Example: Synchronous Reset D-Flip flop , Asynchronous Reset D-Flip flop

Lecture 61 Example : T-Flip Flop

Lecture 62 Example : Master-slave JK Flip Flop

Lecture 63 Example: Counter

Lecture 64 Example: UP/Down Counter

Lecture 65 Example: clock divider using counter- Divide by 2,4,8,....

Lecture 66 Example: Pulse Generator: Mod-3 pulse generator

Lecture 67 Example: Divide by 3 clock

Lecture 68 Example : Ring Counter vs Jonson Counter

Lecture 69 Example : Shift Registers : SISO, SIPO, PISO,PIPO

Lecture 70 Example: LFSR (Linear Feedback Shift Register)- Random Generator

Lecture 71 memory design

Section 10: Switch level modeling

Lecture 72 Switch level modeling

Section 11: Test bench

Lecture 73 Functional simulation

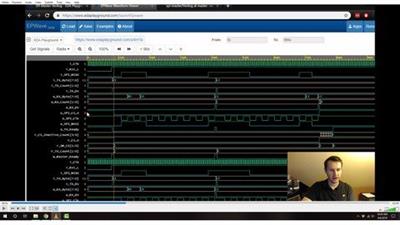

Lecture 74 Example - Test bench for counter design

Lecture 75 Example - Test bench for Pulse generator

Section 12: Functions & Task and system tasks

Lecture 76 Functions & tasks and system tasks

Lecture 77 File based system tasks and random generator system task

Lecture 78 Read file and write in to memory system task

Lecture 79 Programming Language Interface

Section 13: FSM

Lecture 80 FSM Topics

Lecture 81 Why FSM

Lecture 82 What is FSM

Lecture 83 Hardware Realization of FSM : Component or Modules in FSM

Lecture 84 Types of FSM and Mealy Moore FSM differences

Lecture 85 Example : Mealy FSM

Lecture 86 Example: Moore FSM

Lecture 87 Example: Verilog HDL for Mealy FSM

Lecture 88 Example: Verilog HDL for Moore FSM

Lecture 89 Hands-on : Verilog HDL for Mealy FSM and run the execution

Lecture 90 Example: Divide by 2 clk using FSM

Lecture 91 Example: Divide by 3 clk using FSM

Lecture 92 Example: 33 perecent duty cycle clock generation using FSM

Section 14: Sequence detector using FSM with complete Design & TB

Lecture 93 Sequence detector using FSM with complete Design & TB

Lecture 94 Sequence detector using FSM output waveform

Section 15: Project 1: Memory controller

Lecture 95 Memory controller with Design & TB

Section 16: Project 2: FIFO

Lecture 96 FIFO Lecture

Lecture 97 Introduction to FIFO

Lecture 98 Write Read Operation of Normal RAM

Lecture 99 FIFO I/O (input & Outputs)

Lecture 100 Block Diagram and Architecture of FIFO

Lecture 101 Connection of FIFO design & Test bench environment

Lecture 102 Verilog HDL for FIFO design

Lecture 103 Verilog HDL code for FIFO Test Bench

Lecture 104 Run the simulation and finding errors and Analyze the waveform Results

Section 17: Project 3 : Hamming code complete Design & TB for error detection & correction

Lecture 105 Hamming code complete Design & TB for error detection & correction

Section 18: FPGA

Lecture 106 FPGA

Undergraduate Electronics and computer science eeering students,Graduate students who planning their career in VLSI domain front end (Design & verification),Advanced under graduate students, who willing to do project in front end VLSI design

HomePage:

Https://anonymz.com/https://www.udemy.com/course/digital-design-using-verilog-hdl-programming-with-practical/DOWNLOAD

uploadgig.com

https://uploadgig.com/file/download/BA7b8631eA5c5337/f2yTs23H__Complete_V.part1.rar

https://uploadgig.com/file/download/Eb1252641730b6a3/f2yTs23H__Complete_V.part2.rar

https://uploadgig.com/file/download/5c6c1f35ec6744ae/f2yTs23H__Complete_V.part3.rar

https://uploadgig.com/file/download/67ea3c50C8b885DF/f2yTs23H__Complete_V.part4.rar

rapidgator.net

https://rapidgator.net/file/19caabbd0a6f31bae3e4394d0fd5c94d/f2yTs23H__Complete_V.part1.rar.html

https://rapidgator.net/file/353353c177a13e3a67bab8fc32328851/f2yTs23H__Complete_V.part2.rar.html

https://rapidgator.net/file/27c269b1acc0dbfc47d2f1d77a03c707/f2yTs23H__Complete_V.part3.rar.html

https://rapidgator.net/file/af4216b3544799cf12877d7ab6775963/f2yTs23H__Complete_V.part4.rar.html

nitro.download

https://nitro.download/view/114B5C05E7D3382/f2yTs23H__Complete_V.part1.rar

https://nitro.download/view/1248EAF5B92116E/f2yTs23H__Complete_V.part2.rar

https://nitro.download/view/0BBF7439C339FDD/f2yTs23H__Complete_V.part3.rar

https://nitro.download/view/6BFDA6FCC45C1EB/f2yTs23H__Complete_V.part4.rar

Related News

System Comment

Information

Users of Visitor are not allowed to comment this publication.

Users of Visitor are not allowed to comment this publication.

Facebook Comment

Member Area

Top News